**Hardware Architecture Description – Revision 1.0**

# **Trusted Mobile Platform**

# **Hardware Architecture Description**

10/27/2004

Trusted Mobile Platform NTT DoCoMo, IBM, Intel Corporation

File Name: TMP\_HWAD\_rev1\_00\_20040405.doc

**Hardware Architecture Description - Revision 1.0**

### **Trusted Mobile Platform**

# Hardware Architecture Description

Rev. 1.00 June 23, 2004

# Copy Right Notice

Copyright © 2002-2004, Intel Corporation, International Business Machines Corporation, NTT DoCoMo, Inc. All Rights Reserved.

### **Status**

This is a stable revision of the Trusted Mobile Platform Hardware Architecture Description that was agreed upon by Trusted Mobile Platform Promoters.

**Hardware Architecture Description – Revision 1.0**

# Contents

| CON   | NTENTS                                             | 2  |

|-------|----------------------------------------------------|----|

| 1. IN | TRODUCTION                                         | 6  |

| 2. RE | ELATED DOCUMENTS                                   | 7  |

| 3. DE | EFINITIONS AND ABBREVIATIONS                       | 8  |

| 4. AF | RCHITECTURE OVERVIEW                               | 10 |

| 4.1   | 1. ONE PROCESSOR ARCHITECTURE                      | 11 |

| 4.2   | 2. Two Processor Architecture                      | 11 |

| 4.3   | 3. DEFINITION OF THE SECURITY BOUNDARY             | 12 |

|       | 4.3.1. Application Processor                       | 13 |

|       | 4.3.2. TPM                                         | 14 |

|       | 4.3.3. Platform Core Root of Trust for Measurement | 15 |

|       | 4.3.4. System Memory and Memory Controllers        | 15 |

|       | 4.3.5. DMA Controller                              | 16 |

|       | 4.3.6. SIM                                         | 16 |

| 4.4   | 4. Levels of Security                              | 16 |

| 5. PL | LATFORM ROOT OF TRUST                              | 18 |

|       | 1. Requirements                                    |    |

| 5.1   |                                                    |    |

| 5.2   | 2 CORE ROOT OF TRUST FOR MEASUREMENT               | 19 |

| 5.3   | 3 CRTM LIFECYCLE                                   | 20 |

| 5.4   | 4 INTERFACING WITH THE PLATFORM ROOT OF TRUST      | 20 |

| 5.5   | 5 MEMORY TECHNOLOGY FOR THE ROOT OF TRUST          | 21 |

| 5.6   | 6 CRTM OPERATING ENVIRONMENT                       | 21 |

| 5.7   | 7 TRUSTED BOOT HARDWARE                            | 21 |

| 6. TR | RUST MODULE - TPM                                  | 22 |

| 6.1   | 1. REQUIREMENTS                                    | 23 |

| 6.2   | 2. CRYPTOGRAPHIC ENGINES                           | 24 |

| 6.3   | 3. PLATFORM CONFIGURATION REGISTERS                | 25 |

| 6.4   | 4. KEY STORAGE                                     | 25 |

**Hardware Architecture Description – Revision 1.0**

| 6.5. TRUST MODULE PROCESSOR                             | 26 |

|---------------------------------------------------------|----|

| 6.6. MONOTONIC COUNTER                                  | 27 |

| 6.7. ATOMIC OPERATIONS                                  | 27 |

| 6.8. CRYPTOGRAPHIC ALGORITHMS                           | 28 |

| 6.9. TPM DEVIATIONS FOR TRUSTED MOBILE DEVICES          | 29 |

| 7. PROCESSOR SECURITY FEATURES                          | 30 |

| 7.1. Introduction                                       | 30 |

| 7.2. SECURITY CLASS 1                                   | 30 |

| 7.3. SECURITY CLASS 2                                   | 31 |

| 7.4. SECURITY CLASS 3                                   | 31 |

| 7.4.1. Requirements                                     | 32 |

| 7.5. Possible Approaches to Class 3 Security Processors | 33 |

| 7.5.1. Physical partitioning                            | 33 |

| 7.5.2. Virtual Partitioning                             | 33 |

| 7.6. CPU PERIPHERALS                                    | 33 |

| 8. TRUSTED I/O                                          | 34 |

| 8.1. INTEGRATED DEVICE / EXTERNAL DEVICE                | 35 |

| 8.2. INPUT DEVICES                                      | 37 |

| 8.2.1. Biometrics                                       | 37 |

| 8.3. OUTPUT DEVICES                                     | 37 |

| 8.3.1. General Display Unit                             | 37 |

| 8.3.2. Trust Mode Indicator                             | 38 |

| 8.4. SUMMARY OF TRUSTED I/O AND SECURITY LEVELS         | 38 |

| 8.5. SD CARD                                            | 38 |

| 8.5.1. SD card overview                                 | 38 |

| 8.5.2. Secure Key Storage                               | 39 |

| 8.5.3. Integrity protection of processing unit          | 39 |

| 8.5.4. Content Encryption – Recording device            | 39 |

| 8.5.5. Content Encryption – Playback device             | 40 |

| 9. PHYSICAL AND ENVIRONMENTAL PROTECTION                | 40 |

| 9.1. PACKAGING                                          | 41 |

| 9.2. EXTERNAL INTERFACES                                | 43 |

| 9.3. VOLTAGE & TEMPERATURE PROTECTION                   | 44 |

**Hardware Architecture Description – Revision 1.0**

| 10. PERIPHERAL DEVICES                                         | 45 |

|----------------------------------------------------------------|----|

| 10.1. Overview                                                 | 45 |

| 10.2. REQUIREMENTS                                             | 46 |

| 10.3. SIM/USIM                                                 | 47 |

| 10.3.1. SIM Interface (Access / Readers)                       | 48 |

| 10.3.2. Analysis of the USIM and Security Level                | 49 |

| 10.4. BIOMETRIC AUTHENTICATION                                 | 50 |

| 10.4.1. Biometrics Introduction                                | 50 |

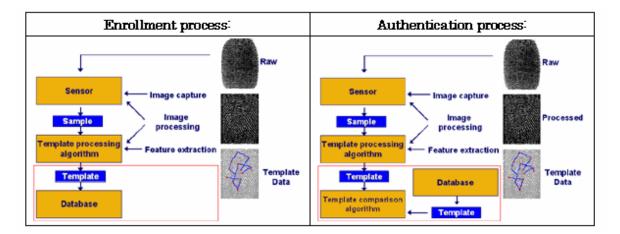

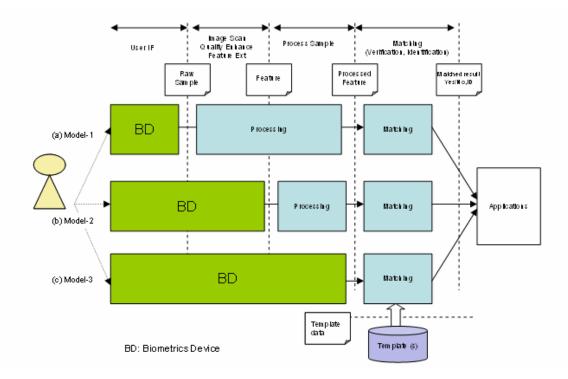

| 10.4.2. Biometric Device Implementation Model                  | 52 |

| 10.4.3. Security Implication and Requirements                  | 54 |

| 10.4.4. Summary of Biometric Systems and Security Level        | 56 |

| 10.5. EXTERNAL MEMORY DEVICES                                  | 57 |

| 10.5.1. External Memory Device Introduction                    | 57 |

| 10.5.2. Security Implication and Requirements                  | 58 |

| 10.5.3. Summary of Smart Memory card System and Security Level | 60 |

| 10.6. REQUIREMENTS FOR GENERAL PERIPHERAL DEVICES              | 61 |

| 10.6.1. Requirements                                           | 61 |

| 10.6.2. Summary                                                | 62 |

| APPENDIX A. CHANGE HISTORY (INFORMATIVE)                       | 63 |

**Hardware Architecture Description – Revision 1.0**

### 1. INTRODUCTION

The Trusted Mobile Platform initiative defines a comprehensive end-to-end security architecture for mobile wireless devices. It consists of the hardware architecture, the software architecture, and the protocol specifications. The Hardware Architecture Description (HWAD) and the Software Architecture Description (SWAD) define a generic architecture for Trusted Mobile Devices (TMD). This document describes the hardware components that are necessary to create TMDs. Some of these software components also bridge the security features with the protocol defined in the protocol specifications.

The architecture defined herein is based upon the prior work performed in the Trusted Computing Platform Alliance (now the Trusted Computing Group) but extends and modifies the basic concepts for low power, handheld devices with limitations on available MIPS and memory. In addition, the concept of trust levels is introduced. Manufacturers and carriers can make their own decisions based upon guidance found in the Trusted Mobile Platform documents as to what trust level is appropriate for the services they choose to deploy. This document does not define implementation specifics. A variety of technology options could be used to build a TMD that supports the architecture defined here.

This document is organized as follows. Section 2 lists related documents and standards. Section 3 provides a list of acronyms and their definitions. Section 4 describes the overall architecture for the trusted platform and defines the components that impact system trustworthiness. Sections 5 through 10 describe in more detail the individual components that make up the trust system. Section 5 describes the platform root of trust. Section 6 describes the Trusted Platform Module (TPM), the functionality required and implementation options. Section 7 defines the security features required for a secure processor that can enforce hardware domain separation between trusted and untrusted applications. Section 8 describes the requirements to protect the data paths between the CPU and TMD input and output devices. Section 9 describes physical and environmental protection features that should be applied to a

Hardware Architecture Description - Revision 1.0

TMD. Section 10 describes peripheral devices that have a potential impact on the security of the TMD.

### 2. Related Documents

- [1] FIPS PUB 140-2 Security Requirements for Cryptographic Modules

- [2] FIPS PUB 180-1 Secure Hash Standard

- [3] FIPS PUB 197 Advanced Encryption Standard

- [4] FIPS PUB 46-3 Data Encryption Standard

- [5] RFC 1321 The MD5 Message Digest Algorithm

- [6] PKCS #11 Cryptographic Token Interface Standard

- [7] RFC 2119

- [8] Trusted Computing Group (TCG) Design Philosophies and Concepts Version 1.0

- [9] Trusted Computing Group (TCG) Main Specification Version 1.1b, <a href="http://www.trustedcomputinggroup.org/">http://www.trustedcomputinggroup.org/</a>, February 2002 (also known as Trusted Computing Platform Alliance (TCPA) Main Specification Version 1.1b)

- [10] TCG Software Stack (TSS) Specification Version 1.0

- [11] Trusted Mobile Platform Security Requirements

- [12] Trusted Mobile Platform Protocol Specification Document

- [13] 3GPP TS 31.101: "UICC-Terminal Interface; Physical and Logical Characteristics".

- [14] 3GPP TS 31.102: "Characteristics of the USIM Application".

- [15] 3GPP TS 33.102: " 3G Security; Security architecture".

- [16] 3GPP TS 11.11: "Specification of the Subscriber Identity Module Mobile Equipment Interface

- [17] 3GPP TS 51.011: "Specification of the Subscriber Identity Module Mobile Equipment Interface".

- [18] TS 03.20: "Digital cellular telecommunications system (Phase 2+); Security related network functions".

- [19] TS 23.048: "Security mechanisms for the (U)SIM application toolkit".

- [20] "BioAPI Specification Version 1.1", March 16, 2001, The BioAPI Consortium, http://www.bioapi.org.

- [21] S. Prabhkar, S. Pankanti, A. Jain, "Biometric Recognition: Security and Privacy Concerns", IEEE Security and Privacy, March/April 2003, pp33-42.

Hardware Architecture Description - Revision 1.0

- [22] "Content Protection for Recordable Media Specification: SD Memory Book Common Part", Rev 0.96, Nov. 26, 2001, by Intel, IBM, Matsushita, and Toshiba

- [23] Trusted Mobile Platform Software Architecture Description

### 3. Definitions and Abbreviations

For the purpose of this document, the following definitions apply:

- **2G** 2<sup>nd</sup> Generation

- **3G** 3rd Generation

- **AES** Advanced Encryption Standard

- **AKA** Authentication and Key Agreement

- **AuC** Authentication Center

- **AUTN** Authentication Token

- **BD** Biometric Devices

- **BIS** Boot Integrity Services

- **BIU** Bus Interface Unit

- **CK** Cipher Key (in 3G)

- **COTS OS** Commercial off-the-shelf Operating System

- CRTM Core Root of Trust for Measurement

- **DES** Data Encryption Standard

- **DIR** Data Integrity Registers

- **DMA** Direct Memory Access

- **GSM** Global System for Mobile Communications

- **HLR** Home Location Register

- **ICC** Integrated Circuit Card

- **IK** Integrity Key

- **IPC** Inter Process Communications

- **K** USIM Individual Key (in 3G)

- **Kc** Ciphering Key (in 2G)

- Ki Individual Subscriber Authentication Key (in 2G)

- **LCD** Liquid Crystal Display

- **LPAR** Logical Partition

- **MCM** Multi-chip Module

- **ME** Mobile Equipment

Trusted Mobile Platform

Hardware Architecture Description – Revision 1.0

| MATT                                                           | I. Momory Management Unit                                            |  |  |

|----------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| MMU                                                            | , ,                                                                  |  |  |

|                                                                |                                                                      |  |  |

|                                                                | Monotonic Counter  Non volatile                                      |  |  |

|                                                                | Non-volatile                                                         |  |  |

| OLED                                                           |                                                                      |  |  |

|                                                                | Platform Configuration Register                                      |  |  |

| PID                                                            | ,                                                                    |  |  |

|                                                                | Personal Identification Number                                       |  |  |

|                                                                | Platform Root of Trust                                               |  |  |

| ROT                                                            |                                                                      |  |  |

| RAND                                                           | RANDom number (used for authentication)                              |  |  |

| RES                                                            | User RESponse bit signed RESponse that is the output of the function |  |  |

|                                                                | f2 in a 3G AKA                                                       |  |  |

| ROT                                                            | Root of Trust                                                        |  |  |

| RSA                                                            | RSA Rivest, Shamir, Adleman                                          |  |  |

| RTM                                                            | RTM Root of Trust for Measurement                                    |  |  |

| RTR                                                            | 1 0                                                                  |  |  |

| RTS                                                            | Ö                                                                    |  |  |

| SHA                                                            | Secure Hash Algorithm                                                |  |  |

| SGSN Serving GPRS Support Node                                 |                                                                      |  |  |

| SIM                                                            | J                                                                    |  |  |

| SN Serving Network                                             |                                                                      |  |  |

| SRES Signed RESponse. Authentication value returned by the SIM |                                                                      |  |  |

|                                                                | the USIM in 2G AKA                                                   |  |  |

| TBC                                                            | Trusted Boot Code                                                    |  |  |

| TBH Trusted Boot Hardware                                      |                                                                      |  |  |

| TCG                                                            | Trusted Computing Group                                              |  |  |

| TCPA                                                           | CPA Trusted Computing Platform Alliance                              |  |  |

| TMP Trusted Mobile Platform                                    |                                                                      |  |  |

| TP                                                             | TP Trusted Platform                                                  |  |  |

| TPA                                                            | PA Trusted Platform Agent                                            |  |  |

| TPM                                                            | <b>TPM</b> Trusted Platform Module                                   |  |  |

| TSS                                                            | SS TPM Support Software                                              |  |  |

| UICC                                                           | CC UMTS IC Card                                                      |  |  |

**Hardware Architecture Description – Revision 1.0**

**USIM** Universal Subscriber Identity Module

**USB** Universal Serial Bus

**VLR** Visitor Location Register

**XRES** Expected RESponse. Authentication value delivered by the 3G

HLR/AuC

### 4. Architecture Overview

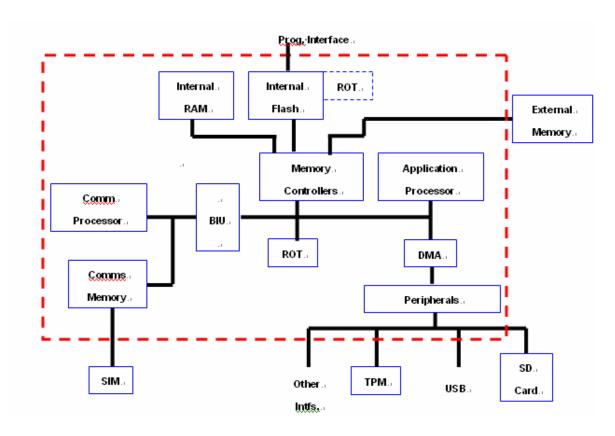

The hardware architecture of a TMD generally consists of 1) a CPU that provides platform control, runs the Operating System (OS), runs a variety of software applications, manages the user interface, interfaces to memory, interfaces to external devices, and supports the communication channel with the appropriate protocols and security. One architectural option is based on a single CPU that performs all of these functions. More complex architectures use two CPUs, with the second CPU generally dedicated to support the communications channel and over-the-air interface. 2) System NV storage; this is generally flash technology, 3) system RAM, 4) memory controllers for the flash and RAM memories, 5) DMA controller, 6) interrupt controller, 7) clock circuits, including a real time clock, 8) keypad and display controllers 9) communications interfaces including over-the-air interfaces like Bluetooth or ISO 14443 and 10) miscellaneous logic.

In addition to these components, GSM phones also have an interface to a SIM. The SIM provides security services for user identity and for channel security. The SIM also can be used for secure storage.

To improve the security of the TMD, a Trusted Platform Module (TPM) or the functional equivalent of the TPM as defined by [9] must be added along with hardware needed to execute a secure boot operation. These components ensure that the Trusted Mobile Device executes a trusted boot process at power up so that the TMD always boots into a trusted environment.

**Hardware Architecture Description - Revision 1.0**

### 4.1. One Processor Architecture

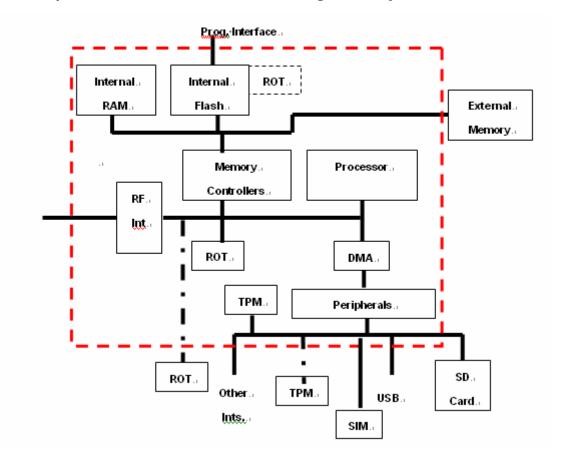

Figure 4-1 shows a generic one processor architecture for a handheld device. Components residing inside the red dotted line indicate components that might reasonably be integrated into a single device. The Core Root of Trust for Measurement technology could be an integrated ROM, part of the flash memory, or a discrete ROM. Similarly, the TPM could be embodied as an integrated component or a discrete TPM.

Figure 4-1 One Processor Architecture

### 4.2. Two Processor Architecture

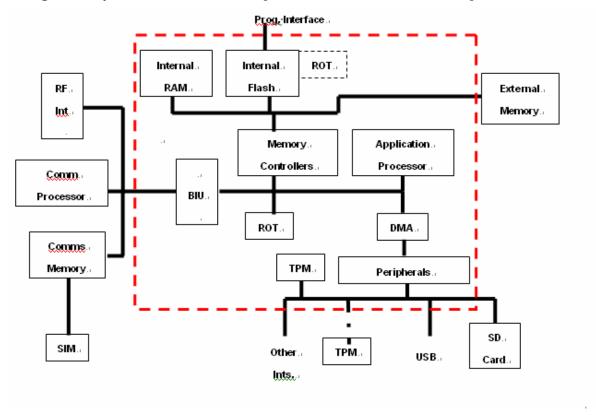

Figure 4-2 shows a generic two processor architecture for a TMD. The implementation options regarding the CRTM and TPM are identical to the options for the one processor architecture. The advantage derived from adding a second processor is the potential to cleanly separate applications from communications processing. This model

**Hardware Architecture Description - Revision 1.0**

significantly reduces the risk of compromise to the communications processor.

Figure 4-2 Two Processor Architecture

## 4.3. Definition of the Security Boundary

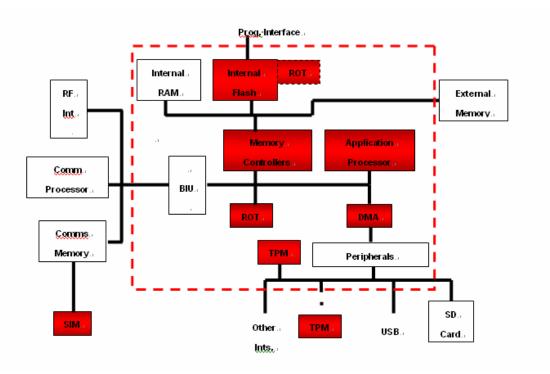

The security boundary consists of those components that impact the trust/security operations performed by the TMD. The components that comprise the security architecture for the two processor system are highlighted in red in Figure 4-3 below.

**Hardware Architecture Description - Revision 1.0**

Figure 4-3 Security Boundary

The components that make up the trust boundary include 1) the application processor 2) the TPM 3) the SIM 4) The CRTM (could be a discrete device or part of another device) 5) NV memory (internal flash), 6) the memory controllers 7) DMA controller. The rationale for including each of these inside the hardware trust boundary is contained in the following sections.

### 4.3.1. Application Processor

In this architecture, the Application Processor plays a role in many security and trust operations. At cold start, trusted boot is executed under control of the application processor. After boot, the application processor executes trusted and untrusted applications and in a trusted system, isolates and protects the data associated with trusted applications. The application processor also interfaces with security peripherals like the TPM, SIM, or a biometric input device.

The main security mechanism that the application processor must provide is protection

**Hardware Architecture Description - Revision 1.0**

of trusted applications and their data from untrusted applications. The current generation of CPUs used in handheld applications does not provide this feature, and many existing handheld OS's are not designed to take advantage of domain isolation hardware if it did exist. In addition, there may be other implementation options that may be used to provide domain isolation without modifications to the CPU.

### 4.3.2. TPM

The Trusted Computing Group (TCG) in [9] has defined the functionality and interfaces for a trust device call the Trusted Platform Module (TPM). The TPM provides a protected execution environment where secrets can be processed without being exposed, secure and hidden storage, and cryptographic engines needed to measure the integrity and validate the source of software residing on the platform. The TPM works closely with the CRTM to perform trusted boot. The TPM cryptographic engines are used to measure and validate the hardware and/or software configurations of the platform. The TPM can compare these measurements to stored "known good" measurements that are securely loaded onto the device and can use these to validate the platform configuration as trusted or untrusted. These values can also be reported to a remote verifier.

Platform measurements are performed each time a platform is activated from a cold start. At cold start, the Platform's Core Root of Trust for Measurement initiates a trusted boot sequence and uses the TPM to perform the cryptographic measurements based on the Secure Hash Algorithm (SHA-1) and RSA algorithm that prove the platform's integrity and authenticate the source of the platform code. Platform measurements can also be performed at times other than power up and can also measure only a part of the platform HW and SW configuration. For example, the integrity and source of a specific application can be checked each time the application is launched.

The cryptographic capabilities of the TPM can be used for more than just trusted boot. TPM internal storage can be used for protected storage of cryptographic keys that are used by the platform. The TPM cryptographic assets can be used to encrypt sensitive data before it is stored in system memory. The internal TPM described in section 6 also provides a bulk encryption capability that can be used for processes like encryption

**Hardware Architecture Description - Revision 1.0**

of private data before it is stored in system memory or real time encryption of streaming data.

The TMD requires much of the functionality of the [9] defined TPM. However, mobile platforms have limitations with respect to available power, physical area available, and bill of material costs that are more stringent than for desktop platforms. The design of current discrete TPM devices has not fully taken these constraints into account. The Trusted Mobile Platform project will investigate alternatives to discrete TPMs that provide the same essential functionality, but with simplifications that may result in physical and electrical characteristics more compatible with the constraints of handheld devices.

#### 4.3.3. Platform Core Root of Trust for Measurement

The Platform Core Root of Trust for Measurement is functionally ROM storage for the trusted boot code (CRTM). The CRTM performs the initial trust measurements for the platform. On power up, the CRTM is invoked to perform the trust measurements on the remainder of the platform. To accomplish this, the CRTM must be stored with a memory technology that does not allow for the code to be modified. In addition, the platform architecture must ensure that the platform CRTM will be invoked each time there is a power up sequence. If the CRTM can be bypassed, then there is not assurance that the platform has been measured and the platform cannot be trusted.

The Platform CRTM does not need to actually be implemented as ROM technology. Other memory technology (i.e. flash memory) could be implemented so that it is functionally equivalent to a ROM. In the case of flash memory, this means that at least that part of the flash used to store the CRTM must be designed so that once programmed, it cannot be overwritten with new code.

### 4.3.4. System Memory and Memory Controllers

Non-volatile system memory is used to store the OS, applications, drivers, and other essential SW components. NV memory is also used to store data. Data that is not private can be stored in memory without it being encrypted. Private data must be encrypted with the TPM or a software application prior to being stored.

Hardware Architecture Description - Revision 1.0

Encrypting private data before its stored protects the information from being read, but does not protect that data from being modified or moved. The TMD must provide hardware mechanisms that provide domain isolation and protect stored sensitive data from being modified in memory. This requirement may be satisfied in a number of ways, including possible modification to the memory architecture so that data associated with one process is protected from being modified by other processes.

### 4.3.5. DMA Controller

In Security Class 3 level systems, the DMA must be controlled by the trusted kernel. The DMA cannot allow trusted physical memory to be accessed by untrusted applications or by an untrusted OS.

For Security Class 1 and Class 2 level systems (refer to Section 4.4) there are no additional security requirements against the DMA Controller.

#### 4.3.6. SIM

In a GSM phone, the SIM's primary purpose is to authenticate the user to the platform. This authentication approach does not uniquely identify an individual, but does prove that the person physically owning the SIM also knows the password – two of the elements generally required to authenticate a user. The TMD can use the authentication data to establish access control based on the user's identity.

### 4.4. Levels of Security

Different usage models merit different trust solutions based on the value of the service, the threat level, how liability is distributed for theft of the service or item, and the cost that someone will bear to provide a trusted solution. Varying levels of trust can be achieved by choosing different implementation options. The trust levels can be associated with different usage models that require different levels of trust. The trust levels defined for Trusted Mobile Devices are Security Class 1, Security Class 2 and Security Class 3. The major technology components associated with each class can be summarized as follows:

**Hardware Architecture Description - Revision 1.0**

#### Security Class 1 devices

- No hardware security features

- Minimal Software integrity checks

- Closed system architecture limited ability to add new software

- Usage model Very limited secure transactions and payment protocols, cannot validate the state of the platform at boot

#### Security Class 2 devices

- HW Trusted Platform Module implementing a [9] subset. TPM functionality focused on trusted boot and measurement of the platform SW configuration.

- Trusted boot from ROM or equivalent

- Common Criteria level 2 or equivalent

- Usage model Secure transactions and protocols, OTA SW download, can validate the state of the platform at boot

#### Security Class 3 devices

- Hardware and software domain separation

- TPM must be able to make platform measurements available to protocols supporting remote attestations and the ability to exchange platform measurements with remote parties.

- Common criteria level 3 or equivalent

- Trusted Computing Base

- Open system

- Usage model Legally binding digital signatures, systems that require run time protection plus trusted boot, very high value transaction, enterprise remote access.

| Security Feature | Security Level        |                       |                                |

|------------------|-----------------------|-----------------------|--------------------------------|

|                  | Security Class 1      | Security Class 2      | Security Class 3               |

| TPM              | -SW TPM or equivalent | - HW TPM ([9] subset) | -Integrated TPM or MCM         |

| CPU architecture | -No requirement       | - MMU                 | -HW domain separation, trusted |

**Hardware Architecture Description – Revision 1.0**

|                                     |                                                                         |                                                                | DMA                                                  |

|-------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|

| Hardware<br>tamper<br>resistance    | -Interlocking enclosure                                                 | - Tamper evident enclosure                                     | -Sensored enclosure<br>-Trusted I/O                  |

| Integrity and attestation           | -Minimal integrity checks                                               | - Integrity checks and source<br>authentication (Trusted boot) | -Trusted boot -Runtime integrity checks              |

| Domain<br>separation<br>enforcement | -COTS OS separation (user<br>account + process)<br>-Java (JAAS or OSGi) | - Hardened OS<br>- Encrypted memory system                     | -Secure processor architecture -SW domain separation |

| Access control                      | - Discretionary                                                         | - Mandatory + discretionary                                    | -Mandatory + discretionary                           |

| Software<br>certification           | - No certification                                                      | - CAPP EAL 2 or equivalent<br>(No formal certification.)       | -CAPP EAL 3 or equivalent                            |

| User<br>authentication              | -PIN                                                                    | -Passphrase                                                    | -Hardware crypto -Biometrics                         |

| Root of Trust                       | -None                                                                   | -ROM or equivalent                                             | -ROM or equivalent                                   |

| SW Architecture                     | -No TCB                                                                 | -TCB                                                           | -TCB                                                 |

| Secure storage                      | -No                                                                     | - Through encryption                                           | -Encryption & domain separation                      |

| Random number<br>generation         | -SW PRNG (Pseudo Random<br>Number Generator)                            | -HW based PRNG                                                 | - True Random Number Generator                       |

| Environmental protection            | None                                                                    | - Interfaces protected                                         | -Interfaces protected -Voltage and temp. sensors     |

**Table 4-1 Trust Levels**

# 5. Platform Root of Trust

This section describes the hardware components that comprise the Platform Root of Trust. This section defines the roles and responsibilities of the PlatformROT in establishing an initial trusted state for the TMD. It identifies secure ROM storage options for the Core Root of Trust for Measurement (CRTM) which works in conjunction with the hardware Trusted Platform Module (TPM) to perform platform integrity measurements.

Hardware Architecture Description - Revision 1.0

The techniques described in this section to measure and report the integrity of a TMD are based on concepts first developed by the [9].

### 5.1. Requirements

Security Class 3 requirements for the Platform Root of Trust are as follows:

- 5.1. The CRTM must be the first code executed after power is applied to the TMD.

- 5.2. It must not be possible to modify the contents and policies contained in the Core Root of Trust for Measurement.

### 5.1 Trusted Boot

The sole responsibility of the CRTM is to perform initial trust measurements for the host platform. The CRTM must be invoked upon boot-time and will be constituted as a "trusted" process that is executed by the Platform ROT. The CRTM performs boot time operations that gather trust measurements within the designated parameters set by the Platform ROT policies.

### 5.2 Core Root of Trust for Measurement

Platform trust measurements require the existence of trusted components on the platform that perform this function. The [9] defines the Platform Root of Trust as a hardware/firmware component with predefined policies specified in the memory device for Core Root of Trust for Measurement (CRTM). The CRTM is registered within the memory blocks, and must not allow for the policies to be modified. In order for the mobile device's processor to perform these functions for integrity checking on the mobile device, it must meet certain criteria specified within the CRTM. Meeting a criteria level for a trusted environment can be a lengthy and difficult process impacting the architecture design phase for the TMD. In order to achieve a trusted architecture, the architecture must reduce the number of trusted components to the minimum number required to establish a trust statement.

Hardware Architecture Description - Revision 1.0

These polices in the CRTM are comprised of several metrics and require the presence of several components necessary to establish a trust statement of authenticity. These are the Root of Trust for Measurement (RTM), Root of Trust for Reporting (RTR) and or Root of Trust for Storage (RTS). In addition, the platform architecture must ensure that the platform ROT will be invoked each time there is a power cycle sequence. If the ROT can be bypassed, then there is not an assurance that the platform has been measured and the platform cannot be trusted.

### 5.3 CRTM Lifecycle

What follows is an example of a CRTM lifecycle for a mobile device when it is powered on for the first time. In order for the mobile device to enter its trusted state the CRTM is initiated starting the trusted boot sequence. The CRTM WILL conduct several levels of integrity measurements. It performs a measurement process to gather system level metrics and also conducts an integrity test for the intended mobile device owner, as mentioned in the Trusted Mobile Platform Software Architecture document in Section 11 (*User Authentication*).

The Platform Root of Trust confirms the functionality and the trustworthiness of the operating environment and enables the TPM to exchange "trusted" data to be processed within the mobile environment's solid state flash memory and or other means of storage. The mobile device specific information and environment is derived from conducting Root of Trust for Measurement (RTM), Root of Trust for Reporting (RTR) and or Root of Trust for Storage (RTS). Given the normal usage model for mobile devices and their associated "persistent ON state", the mobile device manufacturer has the option to register the trusted mobile device prior to user provisioning.

### 5.4 Interfacing with the Platform Root of Trust

The Root of Trust on the platform is embodied in the TPM. The CRTM has hardware and software interfaces to the ROT. At boot time, the TPM interfaces with the CRTM

Hardware Architecture Description - Revision 1.0

which WOULD be registered in the designated memory boot blocks contained within the TMD's solid state storage. Please reference section 5.5 (Memory Technology for the Root of Trust) for more information in how the TPM interfaces with flash, third party memory structures and/or ROM technologies.

### 5.5 Memory Technology for the Root of Trust

Memory technology used to store the CRTM must be designed so that once programmed, it cannot be overwritten with new code. The concept of designating memory blocks within the internal memory for the CRTM can be referenced in (*Software Architecture Specification – Encrypted File Systems*). Alternative means of memory technology can utilize USIM and or other peripheral devices as the storage medium.

### 5.6 CRTM Operating Environment

The CRTM must be placed in a non-rewritable, protected high security domain within the memory architecture. Permission to rewrite and or alter the CRTM is impossible even with super-user / root privileges. The CRTM allows the authenticity and integrity checking of the boot time parameters, by checking the hardware and software integrity within the trusted mobile device. The CRTM would then interface with the Trusted Boot Hardware.

### 5.7 Trusted Boot Hardware

The trusted boot hardware (TBH) is solely responsible for executing the mobile platform's RTM. The TBH is associated with measurement agents and the TPM. Trusted boot is normally conducted at the boot/power cycle of the mobile device and checks each functional process (PID), determining whether processes can be 'trusted' as they come online. The measurement process takes advantage of the transitive trust model described in greater detail in section 5.1 of the Software Architecture Description (SWAD). All boot time activity is recorded by the TPM in the PCRs and the measurement logs. The [9] refers to this process as an authenticated boot. If the

Hardware Architecture Description - Revision 1.0

process has been altered and has been not properly registered at the time of the trusted boot, the TMD can be in an arbitrary state and that state will be recorded and reported. As stated in the [9], "Process that use secrets are indirectly protected by TP hardware. Secrets can be sent to a platform after the platform's software state has been measured and reported. Stored secrets can be released after the platform's software state has been measured and checked. Reporting, storage and retrieval is carried out by the TPM. A platform's software state includes all software processes. So, if a process relies on the use of secrets, it cannot operate unless it and its software environment are correct." [9]. According to [9], in order for a mobile device to be in a 'trusted state' it needs the following:

- At least one root of trust for measuring integrity metrics.

- Exactly one root of trust for storing and reporting integrity metrics

- At least one Trusted Platform Measurement Store

- At least one item of Validation Data

- Exactly one Trusted Platform Agent

At the stage of each boot time, the RTM or measurement agent computes an overall digest of the table of expected digests and compares the overall digest with the value in the data integrity registers (DIR). If a difference exists at the time of boot than that of what is expected based on the data supplied by a Validation Entity (VE), then the TMD platform cannot be trusted.

### 6. Trust Module - TPM

The TPM as defined by [9] uses a set of cryptographic primitive operations to measure the hardware and software of a platform. In the TMD, the TPM is a trusted security peripheral that is employed by the CRTM during the trusted boot process. The minimal set of capabilities required for a TPM are the RSA and SHA-1 algorithms, a random number source, a monotonic counter, secure internal storage, and a secure processing environment.

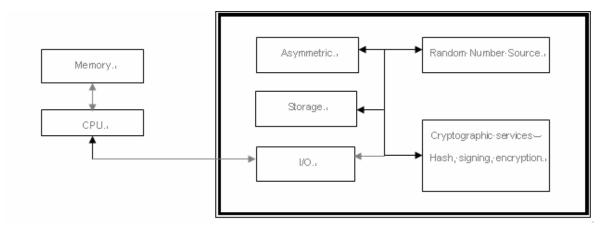

A functional block diagram of a minimal capability TPM is provided in Figure 6-1 below.

Hardware Architecture Description - Revision 1.0

Figure 6-1 TPM Functional Block Diagram

[9] does not specify the implementation of the TPM. Possible embodiments include but are not limited to a software based TPM, a discrete device, or a TPM embedded as part of another device. This specification does link the TPM embodiment to the specific level of TPM security, but a TPM is required in both Security Class 2 and Class 3 security devices. A software-based TPM may be used in Security Class 1 trusted platforms. A hardware based TPM, either discrete or embedded, is required for either Security Class 2 or Class 3 TMDs. Of the two hardware options, the embedded TPM has advantages in cost, performance, electrical interfaces, and physical security.

### 6.1. Requirements

The following requirements apply to the TPM used in a TMD.

- 6.1. The TPM provides secure and hidden storage for TPM secrets

- 6.2. The TPM provides a secure and hidden environment to process secrets

- 6.3. The TPM includes a random number source and the ability to generate keys

- 6.4. The TPM shall include the RSA algorithm for digital signature creation and verification

- 6.5. The TPM shall include the SHA-1 algorithm for hashing

- 6.6. The TPM shall include SHA-1 based HMAC for command authentication

- 6.7. The TPM shall be capable of performing atomic security operations. This

**Hardware Architecture Description - Revision 1.0**

property means that security operations run to completion and that the intermediate results cannot be modified or exposed

- 6.8. The TPM shall include a monotonic counter

- 6.9. The TPM shall provide capabilities for secure key storage and secure data storage. This can be achieved either by storage of unencrypted data inside the TPM boundary or by storing encrypted data or keys in system memory.

For a Trusted Mobile Device, it is also desirable that the TPM have additional characteristics including but not limited to:

- Extensions that allow the minimal set of TPM cryptographic engines (SHA-1, RSA and RNG) to be used to support security protocols

- Additional crypto primitives that allow the TPM to further support standard security protocols. These may include symmetric cryptographic engines), other hashing algorithms like MD5, and support for additional asymmetric algorithms.

- Reduced size and power dissipation. To achieve this, architectures that allow the TPM to be integrated with other devices is permitted.

### 6.2. Cryptographic Engines

The [9] defines a minimal set of cryptographic engines/algorithms that must be supported by the TPM. These include the RSA algorithm and the Secure Hash Algorithm (SHA-1). The TPM used in a Trusted Mobile Device must support these algorithms.

In addition to the minimal set of cryptographic engines, it is desirable that the TPM on the Trusted Mobile Device support additional cryptographic algorithms used by common protocols including but not limited to SSL/TLS, IPSec, Internet Key Exchange (IKE), and content protection among others. Among the most likely algorithms for inclusion are the symmetrical algorithms Advanced Encryption Standard (AES) and the Data Encryption Standard (DES), the hashing algorithm MD5 (Message Digest 5), SHA variants SHA-256, SHA-384 and SHA-512, the Diffie-Hellman (DH) key exchange algorithm and Elliptic Curve Cryptography (ECC).

**Hardware Architecture Description – Revision 1.0**

### 6.3. Platform Configuration Registers

The TPM internal architecture includes 160 bit Platform Configuration Registers (PCRs) that are used to store information about the current state of the platform. [9] specified that TPMs have sixteen PCRs. However, the embedded TPMs for the TMD are only required to have eight 160 bit PCRs.

The PCRs must be volatile registers. This is due to the fact that the platform measurements must be re-started each time the platform is powered up. The TPM must be able to store individual integrity metrics as well as sequences of integrity measurements. Sequences of integrity measurements are stored using the TPM Extend operation. In this operation, the current measurement is concatenated to the present value stored in the PCR being used to store the measurement of the operation. The resulting concatenated value is hashed and the result is stored back to the PCR initially used for storage. This operation assures that at any point in time, the value stored in a PCR is dependent upon both the specific operation being measured and the sequence of measurements preceding that measurement. The TPM QUOTE function can be used to request that information stored in a PCR be output from the TPM.

PCRs must be protected from manipulation of their value by anything other than the TPM itself. For that reason, the PCRs should not be part of the system storage, particularly is TMDs that do not have domain separation hardware and software, but should be part of dedicated TPM storage.

### 6.4. Key Storage

Two types of key storage are required in the TPM. One type of required storage is non-volatile storage used for long term storage of keys or other data. This storage must allow keys to be retained even when power is removed from the device. The second type of key storage is volatile key storage. This is essentially working storage for keys that are currently being used by a TPM.

**Hardware Architecture Description - Revision 1.0**

Non-volatile key storage can be either internal to the TPM, part of the system memory, or could be in both. There are important differences in how keys are stored in the two locations. If a TPM has dedicated internal NV storage, then keys can be stored in their without being encrypted prior to being stored. In this instance, physical protection of the key storage memory by the TPM prevents the keys from being revealed outside the TPM boundary. Alternatively, keys that are stored in system memory do not have the intrinsic physical protection afforded to keys stored in internal TPM memory. As a result, keys that are stored in NV system memory cannot be stored without first being encrypted. TPMs used in TMDs may use either symmetric or asymmetric algorithms to protect keys and other sensitive data. TPMs that do not have symmetric crypto engines must use RSA to encrypt the keys before they are stored in NV system memory. Those TPMs that have symmetrical crypto engines may optionally use the symmetric crypto engine for key encryption. The use of the symmetrical crypto engine results in better throughput and reduced power dissipation. The recommended minimal key size to support these functions is 128 bits for symmetric algorithms and 2048 bits if an asymmetric algorithm is used. In either case, the keys used to encrypt the keys/data being stored in NV system memory must themselves be protected.

Trusted Mobile Device TPMs must have dedicated internal storage for keys that are currently being used by the TPM. The types of keys can include RSA private keys, symmetric keys and HMAC keys. The internal key storage must be dedicated key storage available only to the TPM. Since these keys are unencrypted while being used, they must not be accessible by the rest of the system.

### 6.5. Trust Module Processor

The Trusted Mobile Device TPM must have its own dedicated Trust Module Processor subsystem including the TPM processor, dedicated program memory, dedicated RAM and scratchpad registers. The Trust Module Processor controls all of the internal operations of the TPM. It performs functions such as managing the TPM interface to the system, controlling operation of the TPM crypto engines, processing TPM commands received from the system, managing keys inside the TPM, and performing security checks on the TPM system. The Trust Module Processor ensures that TPM

**Hardware Architecture Description - Revision 1.0**

operations are atomic.

Based on the required functions of the Trust Module Processor, the processor can be relatively primitive. It is essentially a microcontroller that moves data from one crypto engine to another or to/from a crypto engine and memory. Implementation options range from a simple custom microcontroller up to and including full featured CPUs. Cost and power issues favor the use of simple microcontrollers.

A key security requirement satisfied by the Trust Module Processor is that the TPM has a hidden execution environment. Cryptographic processes are executed fully in the TPM using TPM internal memory and the Trust Module Processor. The specific operations, the intermediate results, the cryptographic keys and other sensitive information cannot be observed from outside the device. This requirement applies to both the discrete TPM and for the embedded TPM.

### 6.6. Monotonic Counter

The Trusted Mobile Device TPM must include a monotonic counter (MTC) that can be used by protocols to reduce the threat from replay attacks. There are a variety of implementation options for the MTC including pure software, hardware MTCs based on flash memory technology, and hardware based on counter logic. In any case, the state of the MTC must be non-volatile, must not be able to be manipulated by entities outside the TPM, and must be guaranteed to never repeat values. Note that the MTC is not required to increment in units of "1".

## 6.7. Atomic Operations

The Trusted Mobile Device TPM must be capable of performing atomic operations. This means that a given cryptographic operation is guaranteed to run to completion and that the intermediate results of a primitive operation cannot be modified.

Simple TPM operations may only involve one engine and performing a single operation and are inherently atomic. An example of this is to calculate the hash for a block of

**Hardware Architecture Description - Revision 1.0**

data. In this example, the data is input to the hashing engine; the engine operates on the data and returns the resulting hash. This requirement becomes more complex when multiple engines are involved.

Creating a digital signature is an example of a more complex atomic operation. In this case, atomicity requires that the data being signed in first hashed and then the hash must be provided as an input parameter to the signing engine. In this example, the hash of the data must be contained inside the TPM until it is signed. If the intermediate result, in this case the hash, is exported from the TPM and then subsequently imported for the sign operation, the TSS, TPM driver or other code has an opportunity to substitute a different hash value. If that happens, there is no assurance that the hash being signed corresponds to the hash originally calculated for the message being signed.

### 6.8. Cryptographic Algorithms

The following cryptographic algorithms are required in the TMD TPM.

- RSA for encryption and signing (PKCS#1 v1.5)

- SHA-1 (FIPS 180-1)

The following cryptographic algorithms are optional in the TMD TPM.

- RSA (PKCS#1 v2.1)

- DH key agreement

- ECDH key agreement

- DSA signature

- ECDSA signature

- AES (FIPS 197)

- DES and Triple DES (FIPS 46-3)

- MD5 (RFC 1321)

- SHA-256/384/512

Other cryptographic algorithms may also be provided.

Hardware Architecture Description - Revision 1.0

Refer to the Trusted Mobile Platform Software Architecture Description Section 9.2 for additional information on cryptographic algorithms.

### 6.9. TPM Deviations for Trusted Mobile Devices

Sections 6.1 through 6.7 define areas where the TPM used in the TMD is essentially the same as that defined by the [9]. However, due to the unique constraints in terms of boot time, system performance, power dissipation, operating environment, etc., deviations from the [9] are allowed. Deviations permitted for the TMD include:

- 1. Only 8 PCRs are required

- 2. External key storage and data storage can be based on the use of a symmetric crypto algorithm. If this option is chosen, the AES algorithm in CBC mode with a minimum 128 bit key is recommended.

- 3. The cryptographic algorithms implemented in hardware inside the TMD TPM may be used as accelerators to support security protocols or platform security operations. When used in this mode, the [9] defined authentication protocols (OIAP and OSAP) are not required.

- 4. In addition to the minimal set of algorithms required for [9] interoperability, the TMD TPM may include additional symmetrical, asymmetrical or hashing algorithms including but not limited to DES, TDES, ECC, and MD5.

- 5. Implementation of the full set of TPM commands is not required. The minimal required subset includes:

- TPM\_OIAP (Object Independent Authorization Protocol)

- TPM\_OSAP (Object Specific Authorization Protocol)

- TSS\_Bind

- TPM Unbind

- TPM\_CreateWrapKey

- TSS\_WrapKey

- TSS\_WrapKeyToPCR

- TPM\_LoadKey

- TPM\_EvictKey

- TPM\_GetPubKey

- TPM PCRRead

Hardware Architecture Description - Revision 1.0

- TPM Extend

- TPM\_Quote

### 7. Processor Security Features

It is assumed that all processors of interest will have conventional general-purpose CISC or RISC architectures. Special purpose machines (e.g. Java machines or CLR machines) are not considerations. It is possible to implement a JVM on conventional processors, and it is also possible to extend conventional processors with the ability to interpret Java byte-codes, but these are performance considerations; not security considerations.

### 7.1. Introduction

The fundamental role of a processor in a secure system is to provide isolation. The purpose of isolation is to enable tamper-resistant software execution so that software can process secrets without interference or observation, and can be assured that secrets cannot leak outside its isolation boundary. How strong the isolation provided is, and how much impact on system software architecture can be tolerated depends on how important the security requirements are.

As indicated earlier in this document, three levels of security are defined: Security Classes 1, 2 and 3.. This section discusses the implications to the processor architecture for these three levels.

### 7.2. Security Class 1

Any processor architecture in the market today can support a Class 1 system; there are no specific requirements on the processor architecture.

**Hardware Architecture Description – Revision 1.0**

### 7.3. Security Class 2

Any processor that supports supervisor privilege and virtual addressing can be used to build a Class 2 Security system. This would tend to exclude most Real-time embedded processors, but would include all existing general-purpose processors.

With supervisor mode and virtual addressing, a privileged kernel can isolate any application or service execution in a virtual address space. The actual degree of security (i.e., the strength of the isolation) depends more on a set of complex design trade-offs in the operating system (including its degree of openness). Isolation using virtual address spaces comes at a price in both performance and programming model changes depending on how strong the isolation is. Typically, operating system designs will trade-off complete isolation (thereby decreasing security) in favor of performance. Sometimes this trade-off can be as extreme as executing all code in the same virtual address space. Strong isolation would require that third-party device drivers do not execute in supervisor privilege, and that the only form of interaction between isolated components be of the form of secure Inter-Process Communication (IPC) through the privileged kernel.

Experience has shown that this type of operating system architecture, while meeting the requirements for Class 3 security, suffers from unacceptable performance characteristics, and presents a programming model that is incompatible with the programming models that the majority of existing applications are designed to.

Only if security is an overriding consideration would such an architecture be acceptable. No operating system in the market today has been willing to suffer these performance implications (and model changes) for the sake of security.

### 7.4. Security Class 3

Security Class 3, therefore, not only requires the re-structuring of operating systems, but also requires processor extensions to:

Securely boot into trusted kernel

Hardware Architecture Description - Revision 1.0

- Harden isolation boundaries

- Support legacy programs

- Mitigate performance degradation (optional)

The fundamental goal is to protect the system from any form of software attack.

### 7.4.1. Requirements

A Class 3 Security Processor must provide the facilities that enable the following requirements to be satisfied:

- 7.1. A Trusted Code Base (Trusted Kernel) must be able to control access to all hardware features (particularly physical memory and devices). In particular,

- a. The Trusted Kernel must be able to restrict what physical memory is available to the legacy operating system.

- b. The Trusted Kernel must be able to control what physical memory is accessible through DMA.

- 7.2. The Trusted Mobile Device must securely boot into the Trusted Kernel.

- 7.3. The Trusted Kernel must execute in its own isolated execution environment with access to all processor resources. This execution environment must allow the Trusted Kernel to execute in virtual addressing mode.

- 7.4. The Trusted Kernel must be able to support the execution of a legacy applications and services.

- 7.5. The Trusted Kernel must be able to provide multiple isolated execution environments in which trusted applications and services execute.

- 7.6. The trusted environments must be isolated from each other, and from the legacy execution environments.

- 7.7. The Trusted Kernel must be able to provide a high-performance secure inter-process communication mechanism between trusted and untrusted execution environments and between trusted environments. Thus, an untrusted application must be able to call a trusted service, and a trusted application must be able to call an untrusted service.

- 7.8. On reset, volatile memory used by trusted applications and services must be scrubbed of secrets.

Hardware Architecture Description - Revision 1.0

### 7.5. Possible Approaches to Class 3 Security Processors

The following are two general approaches to Class 3-security processors. Each approach described may be implemented in multiple different ways depending on the base processor architecture that is being extended.

### 7.5.1. Physical partitioning

In this approach, sufficient hardware processor resources are added to allow the physical memory of the platform to be partitioned into multiple separate Domains. The partitioning would be managed by the trusted kernel that executes in its own Domain. Other Domains would be used to execute operating system services, while the remaining domains would be used to execute applications and network data services (with varying degrees of trust). All the requirements (as listed above) should be satisfied.

### 7.5.2. Virtual Partitioning

In this approach, the processor is extended with a traditional general-purpose virtualization architecture. This architecture gives a Virtual Machine Monitor fine-grained control over what physical resources a particular Virtual Machine can access; any violation would result in a trap to the Monitor. In addition to the virtualization extensions, the processor must ensure that the platform securely boots into the Virtual Machine Monitor. The Virtual Machine Monitor creates virtual machines. The Virtual Machine Monitor creates virtual machines. The Virtual Machine Monitor would act as the Trusted Kernel; it would create a separate virtual machine for the execution of each application or network data service.

### 7.6. CPU Peripherals

In addition to the fundamental modifications required to the CPU, any of the architectures described above in Section 7.5 may also require corresponding modifications to the DMA Controller, memory controllers, and Interrupt Controller.

Hardware Architecture Description - Revision 1.0

The implementation of these peripherals must ensure that they cannot be exploited by untrusted operating system services or untrusted applications to gain access to trusted memory space.

### 8. Trusted I/O

The devices that provide the user interface in a Trusted Mobile Device must be trusted. The interactions between the user and the device must be protected or hidden from interception, observation, and hacking. This chapter describes the hardware architecture of Trusted I/O provided by the Trusted Mobile Device.

The following sets of trusted input/output requirements apply to the Trusted Mobile Device.

- 8.1. The Trusted Mobile Device shall be able to display trusted messages on the display

- 8.2. The Trusted Mobile Device shall provide an indicator to the operator that is activated only when the displayed message is trusted.

- 8.3. The Trusted Mobile Device shall provide security mechanisms that ensure that trusted input (i.e. from a keyboard) is received by the TMD without any modification, deletion, or addition to the input data stream. Security mechanisms to be employed may include hashing or encryption of the message or data being input

- 8.4. Independence of I/O device. The wiring signal of the I/O devices used by the Trusted Mobile Device should be separated from other parts of the device.

The I/O devices used in Trusted Mobile Devices are listed in Table 8-1. In the handheld device, the standard input method is finger input device and LCD devices are widely used as the general display unit. Here, the Trusted Mode Indicator (TMI) is a special device used only by the Trusted Mobile Device.

Table 8-1 Trusted I/O Devices

|  | Category | Used device | Security consideration |

|--|----------|-------------|------------------------|

|  |          |             |                        |

Hardware Architecture Description - Revision 1.0

| Input  | Finger input                          | Key pad, touch panel | Used for PIN, password input                                                 |

|--------|---------------------------------------|----------------------|------------------------------------------------------------------------------|

|        | Pointing device                       | Cursor, pen          |                                                                              |

|        | Sound                                 | Microphone           | Voice recognition                                                            |

|        | Image                                 | Camera               | Face recognition                                                             |

|        | Biometrics                            | Fingerprint scanner  | Authentication                                                               |

| Output | Bitmap display (General Display Unit) | LCD, OLED            | Common display device. Must provide a Trusted Display Mode (works with TMI). |

|        | Indicator                             | LED                  | Can be used as Trusted Mode Indicator.                                       |

|        | Sound                                 | Speaker              | Possible auxiliary TMI                                                       |

### 8.1. Integrated Device / External Device

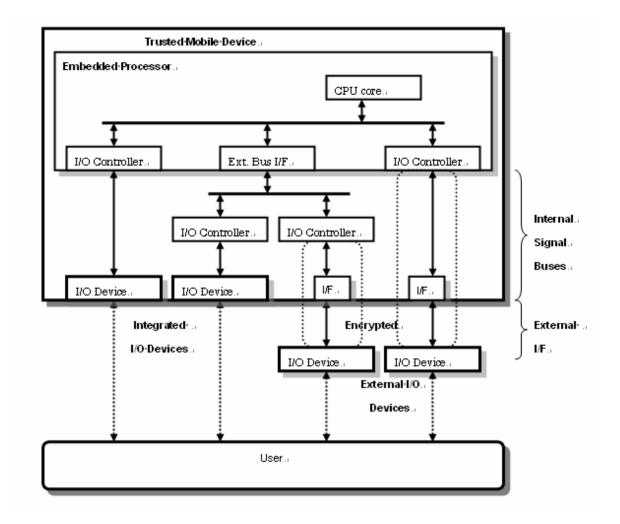

Figure 8-1 shows the block diagram of a typical Trusted Mobile Device. A TMD has both integrated input and output devices. For example the keypad is just buttons and is wired to its controller, which in many cases is embedded in the CPU chip. A malicious attacker may open the device and insert some kind of eavesdropping device. This is very difficult and requires advanced techniques. If the device has a tamper resistant or sealed packaging implementation, these kinds of attacks are made more difficult. The embedded processor used by a TMD may provide a built-in I/O interface, e.g., an LCD controller, touch panel controller, and keypad interface. Alternately, a discrete I/O interface chip on the peripheral bus may be used. The internal signal between the interface and the device should be routed directly between the source and destination and should not be accessible from the surface of the board to prevent malicious access. Independence of the I/O devices is also required for a Security Class 3 device.

An external I/O device can be attached to the Trusted Mobile Device. If we allow it to process sensitive data or information, a reliable cryptographic mechanism is required to

**Hardware Architecture Description – Revision 1.0**

protect the data passing through the interface. Furthermore, an external I/O device must itself be a tamper resistant/evident device and have the same security level as the TMD or otherwise, the external I/O device must not handle sensitive information. Mutual authentication between such a trusted external I/O device and the Trusted Mobile Device must be performed. If encryption is used to protect the interface to external devices, the encryption device inside the TMD must also be secure, and it should be part of either the TPM or the Trusted Computing Base.

Figure 8-1 Implementation example of the Trusted User Interface Device

Hardware Architecture Description - Revision 1.0

## 8.2. Input Devices

Keypads or touch panels are widely used as finger input devices. These devices are also used for password entry. When a device is used to handle such kinds of sensitive data, any input data entered by a user must be protected from malicious attacks. The left side of Figure 8-1 roughly shows the block diagram of an integrated input device. Physical tampering attacks against the internal signal buses between devices and controllers must be prevented. To prevent this kind of attack, tamperproof seals or tamper-resistant packaging must be used for the device. Security Class 3 Trusted Mobile Devices must provide this protection.

#### 8.2.1. Biometrics

This is an optional user authentication mechanism based on biometric information about legitimate users. These features add authentication flexibility and reduce the exposure of a PIN or pass phase in public areas. They also allow for individuals to be identified to a platform as opposed to a device being identified to a platform. This allows the Access Control policy to be tied to a specific user, even if a device is shared. The security requirements for the biometric devices are same as for other I/O devices. Microphones or cameras can also be used as biometric devices.

# 8.3. Output Devices

The Trusted Mobile Device can have several output devices listed in Table 8-2.

# 8.3.1. General Display Unit

A flat-panel device such as an LCD (Liquid Crystal Display) or an OLED (Organic Light-Emitting Diode) is widely used as a graphical user interface device. The device has a frame buffer memory to store the screen image and is controlled by the TCB. The DMA controller periodically copies the data from the frame buffer to the LCD controller. Thus, the steps of this operation should be trusted. Memory separation and Trusted DMA are used to achieve this requirement.

Hardware Architecture Description - Revision 1.0

#### 8.3.2. Trust Mode Indicator

A Trusted Mobile Device must support a Trusted Mode Indicator (TMI). There are several implementation choices to achieve this requirement. See also the Trusted User Interface Chapter in the Trusted Mobile Platform Software Architecture Document. This indicator must be controlled by the TCB.

# 8.4. Summary of Trusted I/O and Security Levels

Table 8-2 Trusted I/O for each Security Level

|                                                                     | Security Level   |                            |                            |  |  |

|---------------------------------------------------------------------|------------------|----------------------------|----------------------------|--|--|

|                                                                     | Security Class 1 | Security Class 2           | Security Class 3           |  |  |

| Trusted I/O                                                         | No               | Yes                        | Yes                        |  |  |

| Tamper-resistant or sealed<br>package for Integrated I/O<br>devices | None             | Sealed packaging           | Tamper resistant packaging |  |  |

| Trusted Mode Indicator                                              | No               | Yes                        | Yes                        |  |  |

| Secured I/F for External I/O                                        | No               | Yes, if device is used for | Yes, if device is used for |  |  |

| device                                                              |                  | authentication, etc.       | authentication, etc.       |  |  |

# **8.5. SD Card**

This subsection discusses the SD card as an example for secure external storage.

#### 8.5.1. SD card overview

Secure Digital Memory Card, otherwise known as the SD card is a non-volatile memory with digital rights management capabilities, (www.sdcard.org). The SD card enables secure downloading of all types of digital data, (e.g., music, movies, photos, news, e-books, etc). Aside from offering a solution as an external memory device, the SD card

**Hardware Architecture Description - Revision 1.0**

complies with the Content Protection for Recordable Media (CPRM) specification as determined by 4C Entity (<a href="http://www.4centity.com">http://www.4centity.com</a>) to ensure digital rights management.

The CPRM architecture within the SD Card consists of Media Key Blocks (MKB). The MKB is composed of a matrix of encrypted versions of a media key, which is encrypted by a number of Device Keys. Several Device Keys are securely stored in a device.

### 8.5.2. Secure Key Storage

If a Device Key is compromised, the Media Key is compromised. Hence, a TMD shall securely store the Device Keys.

During the processing, several keys are generated. A TMD shall protect the confidentiality and integrity of such keys.

### 8.5.3. Integrity protection of processing unit

A TMD shall protect the integrity of the SD card processing modules resident in the device.

## 8.5.4. Content Encryption – Recording device

Three scenarios are possible how content can be provided to a TMD. Content being encrypted compliant to the SD card, channel encrypted (e.g., SSL/TLS), and plain text content.

- (a) If the content is encrypted compliant to the SD card, the content shall be sent to the SD card as it is.

- (b) If the content is sent through an encrypted channel, the content must be decrypted in the device first, into plain text content before it is encrypted into the SD card. Therefore, the TMD shall protect the confidentiality and integrity of the original

Hardware Architecture Description - Revision 1.0

content after it arrived at the device.

(c) If the content is provided in a plain text to the device, a TMD should not transfer it into the SD card encryption system because there is no assurance if the content is legal.

### 8.5.5. Content Encryption – Playback device

The encrypted content is sent to the playback device. The device decrypts it and renders (or play) it.

- (a) If the rendering device is a hardware component such as an LSI chip which is capable of taking encrypted content directly as an input, and, decrypts it and renders it all inside of the hardware device, there is no chance that the original content is stolen.

- (b) If software modules are used to decrypt the encrypted content and/or to render it, there is a chance for an attacker to steal the content unless the integrity of the processing modules and the confidentiality of the data being processed by the modules are protected.

Therefore, a TMD shall protect the integrity of the playback module and the confidentiality of the plain text content data being transferred.

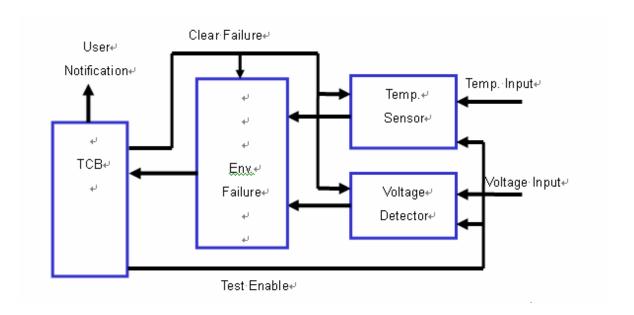

# 9. Physical and Environmental Protection

Physical protection for the TMD includes three types of protections: 1) protection of the interfaces so that attackers cannot gain access to sensitive information on the device including keys and private data, 2) protection against environmental attacks against the platform. These are primarily based on voltage and temperature attacks and 3) protecting the device from being tampered with. This is focused on detecting instances where the handheld device is physically attacked at the package level.

The hardware described in this section must satisfy the following requirements to be considered a Security Class 3 TMD:

Hardware Architecture Description - Revision 1.0

- 9.1. Trusted Mobile Devices shall provide physical evidence of tamper attacks (applicable to all three security levels)

- 9.2. Trusted Mobile Devices shall not perform trusted operations if the package (case) has been opened (applicable to Security Class 2 and Class 3 levels only)

- 9.3. Trusted Mobile Devices shall be able to detect temperature conditions outside the normal operating range of the device and shall not perform trusted operations if the temperature is outside the normal operating range (Security Class 3 TMDs only).

- 9.4. Trusted Mobile Devices shall be able to detect voltage conditions outside the normal operating range of the device and shall not perform trusted operations if the voltage is outside the normal operating range (Security Class 3 only).

- 9.5. External interfaces of security critical components shall be protected so that security critical information cannot be accessed by external probing of the TMD or the packages that make up the device (both Security Class 2 and Class 3 TMDs).

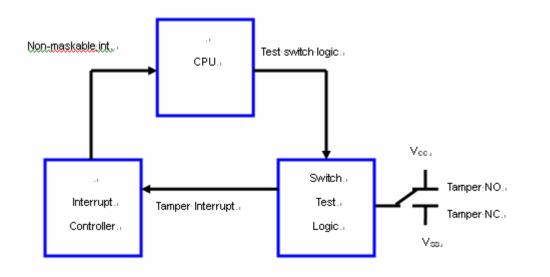

# 9.1. Packaging

The Trusted Mobile Device requires physical protection at the package level. The objective is to protect the TCB and internal security resources from physical tampering or replacement. The three platform trust levels require different protection mechanisms. Security Class 1 level platforms may use only an interlocking enclosure. Security Class 2 security platforms must add tamper evident tamper protection that can be used in conjunction with the interlock switch. At the Security Class 3 level, an interlocking sensor should be employed that can provide an indication to the TCB that the security perimeter has been breached.

For Security Class 1 devices, the interlocking enclosure is similar to the enclosures that are currently used in handheld devices. These enclosures do not have any special security features and the enclosure does not provide any evidence to the user that the device has been attacked. In addition, these enclosures do not have a tamper sensor so that the platform SW cannot be notified that the tamper boundary has been penetrated.

**Hardware Architecture Description – Revision 1.0**

Security Class 2 devices add passive tamper evident protection at the device level. Several technologies can be used to provide tamper evidence including various stickers and protective coatings. The coatings are not intended to actively prevent penetration of the device. Similarly, tamper evident devices are not designed to provide notification to active circuitry that can respond to the tamper event. These devices merely provide evidence to a user that the TMD has been opened and potentially modified in a way that could defeat the trust mechanisms on the platform.